# Hydrogen-Induced Changes in the Breakdown Voltage of InP HEMTs

Roxann R. Blanchard, Jesús A. del Alamo, and Albert Cornet Calveras

Abstract—In this work, electrical measurements show that the breakdown voltage,  $BV_{DG}$ , of InP HEMTs increases following exposure to  $H_2$ . This  $BV_{DG}$  shift is nonrecoverable. The increase in  $BV_{DG}$  is found to be due to a decrease in the carrier concentration in the extrinsic portion of the device. We provide evidence that  $H_2$  reacts with the exposed InAlAs surface in the extrinsic region next to the gate, changing the underlying carrier concentration. Hall measurements of capped and uncapped HEMT samples show that the decrease in sheet carrier concentration can be attributed to a modification of the exposed InAlAs surface. Consistent with this, XPS experiments on uncapped heterostructures give evidence of As loss from the InAlAs surface upon exposure to hydrogen.

*Index Terms*—Electric breakdown, hydrogen, indium compounds, MODFETs, surfaces, X-ray spectroscopy.

#### I. INTRODUCTION

H YDROGEN degradation of III-V FETs is a serious and well-documented reliability concern [1]–[6]. Exposure occurs when hydrogen out-gasses from packaging material and gets trapped inside hermetically sealed packages. Over time, hydrogen causes changes in device characteristics that can ultimately lead to parametric module failures. Compared with more extensive studies of H<sub>2</sub> degradation of GaAs MESFETs and PHEMTs [3]–[6], only limited data on the H<sub>2</sub> sensitivity of InP HEMTs is available [1], [2], [5]. To our knowledge, a device-level solution to this problem has not been reported for either InP or GaAs technologies.

Previous work on the effects of H<sub>2</sub> exposure has focused primarily on the changes in the device threshold voltage,  $V_T$ , and transconductance,  $g_m$  [2]–[6]. These device parameters are governed mainly by the physics in the intrinsic region of the device, which is the area directly beneath the gate. In this work, we report that in addition to this, hydrogen also affects the extrinsic region, the area outside of the gate, and in a manner that is very different from the intrinsic region. We show that the interaction of H<sub>2</sub> with exposed InAlAs in the gate recess region leads to a decrease in the extrinsic sheet carrier concentration,  $n_{s,\text{ext}}$ , causing an increase in the device gate-to-drain breakdown voltage, BV<sub>DG</sub>. Unlike  $V_T$  and  $g_m$ , the change in BV<sub>DG</sub>

R. R. Blanchard is with Analog Devices, Inc., Wilmington, MA 01887 USA. J. A. del Alamo is with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: alamo@mit.edu).

A. Cornet Calveras is with the Department of Applied Physics and Electronics, University of Barcelona, 08028 Barcelona, Spain.

Digital Object Identifier 10.1109/TDMR.2005.846825

is nonrecoverable. These results are consistent with similar experiments reported in AlGaAs/GaAs HEMTs [7].

### **II. EXPERIMENTAL**

The InP HEMTs used for this study were fabricated at MIT. The device heterostructure consists of: semi-insulating InP substrate, 2500 Å InAlAs, bottom  $\delta$ -doping, 50 Å InAlAs spacer, 200 Å InGaAs channel, 20 Å InAlAs spacer, top  $\delta$ -doping, 270 Å InAlAs pseudo-insulator, and a 70 Å undoped InGaAs cap. The fabrication process features a selective cap recess, sidewall recess isolation, dielectric-assisted lift-off, Ni/AuGe/Ni alloyed ohmic contacts, ECR-enhanced, low-temperature Si<sub>3</sub>N<sub>4</sub> passivation and Ti/Pt/Au gate metallization. The devices used in this study have gate lengths from 0.6  $\mu$ m to 10  $\mu$ m, and gate orientations along the [011], [010], and [01T] directions on a (100) substrate.

Hydrogen exposure and characterization measurements were made in a temperature-controlled wafer probe station equipped with a sealed chamber allowing the introduction of N<sub>2</sub> or forming-gas (5% H<sub>2</sub> in N<sub>2</sub>). All devices underwent a thermal burn-in at 230 °C in N<sub>2</sub> until no further changes in threshold voltage,  $\Delta V_T$ , were observed. The devices were then annealed unbiased at 200 °C for 3 hours in forming-gas. For reference, selected burned-in devices were also annealed in N<sub>2</sub>. A detailed room-temperature characterization was performed pre-anneal and post-anneal. To monitor degradation in the extrinsic portion of the device, BV<sub>DG</sub> was measured using the drain-current-injection technique [8]. The breakdown voltage was defined at  $I_G = 1$  mA/mm.

Following  $H_2$  degradation exposure, some devices underwent a subsequent recovery anneal in pure  $N_2$  at 200 °C for up to 24 hours. This recovery anneal is designed to see if  $H_2$  degradation can be annealed out with further thermal processing in pure  $N_2$ . Recovery behavior has been frequently reported following  $H_2$  degradation [1], [4], [5]. BV<sub>DG</sub> was also measured at room temperature following the  $N_2$  recovery anneal.

The behavior of  $V_T$  in these devices as a result of similar hydrogen exposure and follow-on recovery anneals has been described in [2].

## **III. RESULTS**

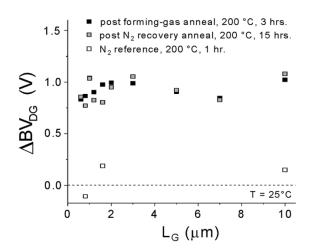

Before annealing, the breakdown voltage of these devices was approximately 6.7 V. After annealing in forming-gas at 200 °C for 3 hours,  $BV_{DG}$  increased on average 0.9 V for all devices, as shown in Fig. 1.  $\Delta BV_{DG}$  showed no  $L_G$  or orientation dependence, in contrast to the  $\Delta V_T$  behavior observed on the same devices [2]. The control devices annealed in N<sub>2</sub> showed no  $BV_{DG}$

Manuscript received July 6, 2004; revised January 6, 2005. This work was supported in part by Sanders Lockheed-Martin and by U.S. Army Research Laboratory Contract DAAD19-02-2-0002. This work made use of MRSEC Shared Facilities supported by the National Science Foundation under Award Number DMR-9400334.

Fig. 1. Black squares show change in  $BV_{DG}$  after exposure to forming-gas (5%  $H_2$  in  $N_2$ ). There is no  $L_G$  dependence, nor was there any orientation dependence in  $\Delta BV_{DG}$ . Data in the gray squares show that the increase in  $BV_{DG}$  does not recover with further annealing in  $N_2$  following the forming-gas degradation anneal. All measurements at room temperature.

increase. The total change in  $BV_{DG}$  for samples that additionally underwent a subsequent recovery anneal in N<sub>2</sub> for 15 hours at 200 °C is also shown in Fig. 1. As seen in Fig. 1,  $BV_{DG}$  does not recover with further N<sub>2</sub> annealing. All these results are consistent with similar experiments reported in AlGaAs/GaAs HEMTs [7]. Devices without Si<sub>3</sub>N<sub>4</sub> passivation were also fabricated and underwent identical experiments. They were found to behave in a similar way.

The increase in  $BV_{DG}$  could be explained with either an increase in the gate Schottky barrier height,  $\phi_B$ , or a decrease in  $n_{s,ext}$  [9]. To produce a 0.9 V increase in  $BV_{DG}$ ,  $\phi_B$  must increase by nearly 15 meV [9]. This is inconsistent with the *negative* threshold voltage shift observed on the same devices following H<sub>2</sub> exposure [2]. It is also inconsistent with the fact that  $\Delta V_T$  was found to recover with further N<sub>2</sub> annealing while  $\Delta BV_{DG}$  did not. Therefore, the increase in  $BV_{DG}$  is a result of a reduction in  $n_{s,ext}$ .

The reduction of  $n_{s,\text{ext}}$  required to realize the increase in  $BV_{DG}$  could occur through donor passivation [3], through changes in the surface in the extrinsic region [10], [11], or through stress-induced piezoelectric charges in the extrinsic region [1], [2]. Previous work has shown that exposure to H<sub>2</sub> leads to compressive stress in Ti/Pt/Au gates due to the formation of TiH<sub>x</sub> [1], [2] and the creation of a piezoelectric volume charge distribution in the device. Piezoelectric charge is ruled out here as the main cause of the  $n_{s,\text{ext}}$  decrease because there is no orientation dependence to  $\Delta BV_{DG}$ .

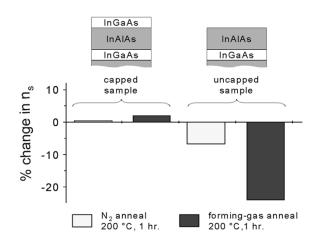

To determine if the decrease in  $n_{s,ext}$  is due to donor passivation or due to changes in the surface stoichiometry, we have directly measured  $n_s$  on Hall measurement samples prepared from the same wafer used to fabricate the transistors. One set of samples retained the InGaAs capping layer. In a second set of samples, the InGaAs capping layer was selectively etched off, exposing the InAlAs insulating layer. An etching process identical to the one used in device fabrication was followed. Hall measurements were performed at room temperature before and after annealing the samples in either N<sub>2</sub> or forming-gas at 200 °C for 1 hour.

Fig. 2. Hall measurements showing the change in  $n_s$  on capped and uncapped HEMT heterostructures. There is no change in  $n_s$  for the capped samples after annealing in either N<sub>2</sub> or forming-gas. In contrast, the uncapped samples in which the InAlAs layer is exposed show an  $n_s$  decrease of >20% after annealing in forming-gas, compared to <10% for the N<sub>2</sub> annealed samples. This rules out donor passivation as the cause of the reduction in  $n_s$  due to H<sub>2</sub> exposure.

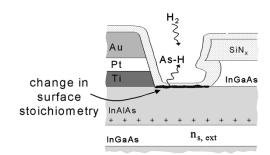

Fig. 3. Cross section of a typical InP HEMT, focusing on the gate region at the drain end of the device. This diagram depicts the proposed mechanism for explaining the reduction of  $n_{s,ext}$  after exposure to H<sub>2</sub>. H<sub>2</sub> reacts with the exposed InAlAs surface and modifies its stoichiometry. This changes the Fermi pinning position at the surface or creates trap states that become subsequently occupied. The end result is a reduction in the sheet carrier concentration in the InGaAs layer underneath.

The results of this experiment are shown in Fig. 2. There was no change in the  $n_s$  for the capped samples under either annealing condition. For the uncapped samples, there was a >20% decrease in  $n_s$  following the forming-gas anneal. The uncapped samples annealed in N<sub>2</sub> showed a decrease in  $n_s$  of less than 10%. Since it is unlikely that the InGaAs cap is a significant barrier to hydrogen diffusion, this experiment allows us to rule out donor passivation as the source of the  $n_s$  reduction in the extrinsic region.

We therefore postulate that changes in the surface potential of the InAlAs layer are responsible for the reduction in  $n_{s,\text{ext}}$ . Some InAlAs is inevitably exposed when part of the InGaAs cap layer is removed so that the gate may directly contact the InAlAs. This is known as the gate-recess region and is illustrated in Fig. 3. A change in the surface potential of the exposed InAlAs could come about through As desorption, leaving behind a cation rich surface [10]. This mechanism can reduce  $n_{s,\text{ext}}$  by changing the Fermi level pinning position at the surface [11] or by creating trap states that become subsequently occupied [7].

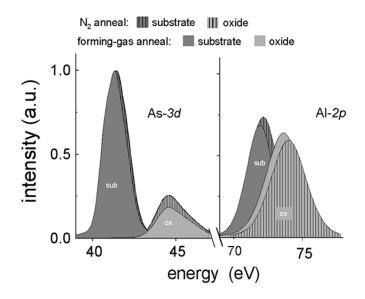

Fig. 4. XPS results comparing uncapped HEMT samples annealed in either N<sub>2</sub> or forming-gas. The As-3*d* data are presented on the left, and show that the As(oxide)/As(substrate) ratio decreases after the forming-gas anneal, relative to the N<sub>2</sub> control sample. In contrast, the Al-2*p* core level spectra on the right show that the Al(oxide)/Al(substrate) peak ratio increases after the forming-gas anneal, relative to the N<sub>2</sub> control sample. These results are evidence showing that exposure to H<sub>2</sub> causes As loss from the InAlAs native oxide. Composite peaks have been deconvolved into their respective oxide and substrate components. All values have been normalized to the peak composite value.

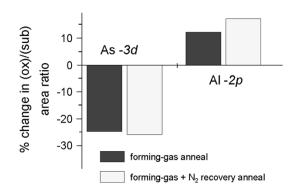

In order to verify this hypothesis, we have performed XPS measurements on uncapped heterostructures nearly identical to those used in the transistor and Hall measurements. The samples were annealed for 1 hour in either N<sub>2</sub> or forming-gas at 200 °C. Selected samples also underwent a subsequent N<sub>2</sub> recovery anneal following the H<sub>2</sub> degradation anneal. The Al-2*p* and As-3*d* core level spectra were examined (the results examining In-3*d* spectra were inconclusive since the In<sub>2</sub>O<sub>3</sub> and InAs bonding energies are too close to be distinguished). The composite peaks were deconvolved into their respective substrate and native-oxide components. All values were then normalized to the peak composite value. The results are shown in Fig. 4.

Examining the As-3d spectra on the left in Fig. 4, we see that the sample annealed in forming-gas showed a 28% decrease in the As(oxide)/As(substrate) total integrated area ratio compared to the N<sub>2</sub> control sample. This indicates that the relative amount of As<sub>2</sub>O<sub>3</sub> at the surface *decreased* for the sample annealed in forming-gas, compared to the sample annealed in N<sub>2</sub>. In contrast, the Al(oxide)/Al(substrate) area ratio for the sample annealed in forming-gas increased by 13% compared to the N<sub>2</sub> control sample, as shown on the right in Fig. 4. This indicates that relative amount of Al<sub>2</sub>O<sub>3</sub> at the surface *increased* for the sample annealed in forming-gas, compared to the sample annealed in forming-gas, compared to the sample annealed in forming-gas, compared to the sample annealed in N<sub>2</sub>.

Fig. 5 is a bar graph comparing the changes in the Al(oxide)/Al(substrate) and As(oxide)/As(substrate) area ratios of samples annealed in forming-gas and a sample that underwent a subsequent  $N_2$  recovery anneal. Both are relative to their respective  $N_2$  control samples. These results show that the InAlAs surface degradation does not recover after further

Fig. 5. Bar graph summarizing the results of XPS measurements of the InAlAs surface after the forming-gas anneal, and after a subsequent recovery anneal in pure N<sub>2</sub> at 200 °C for 15 hours. All numbers are relative to the N<sub>2</sub> control sample. The loss of As from the InAlAs surface does not recover following further annealing in N<sub>2</sub>, consistent with the BV<sub>DG</sub> measurements.

annealing in  $N_2$ , consistent with our electrical measurements of  $\mathrm{BV}_{\mathrm{DG}}$ .

The decrease in the As(oxide)/As(substrate) ratio observed in XPS is evidence of As loss from the native oxide of InAlAs after exposure to  $H_2$ . Similar results have been observed on AlGaAs surfaces [10]. As postulated in [10], the adsorption of H onto the oxidized semiconductor can lead to the formation of volatile AsH<sub>3</sub> with H<sub>2</sub>O as a byproduct [10], [12]. The volatile AsH<sub>3</sub> desorbs, leaving H<sub>2</sub>O on the surface [11].

Physisorbed H<sub>2</sub>O on InGaAs substrates has been shown to lead to additional cation oxidation and further AsH<sub>3</sub> desorption [10], [12]. In the case of InAlAs surfaces, physisorbed H<sub>2</sub>O could result in the formation of additional Al<sub>2</sub>O<sub>3</sub> or In<sub>2</sub>O<sub>3</sub>. However, the heat of formation of Al<sub>2</sub>O<sub>3</sub> is -400 kcal/mol, making it significantly more stable that either In<sub>2</sub>O<sub>3</sub> (-222 kcal/mol) or As<sub>2</sub>O<sub>3</sub> (-156 kcal/mol) [13]. It therefore seems reasonable that Al oxidizes preferentially, which is consistent with our XPS observation of an increase in the Al(oxide)/Al(substrate) peak ratio.

A possible consequence of the removal of As from the InAlAs surface is a modification in the surface stoichiometry. This could change the surface Fermi-pinning position or result in trap states that can subsequently become occupied by electrons. Both would be consistent with a reduction in  $n_s$  [7], [11]. Moreover, this phenomenon is logically not recoverable, consistent with both the XPS and electrical experiments.

# IV. CONCLUSION

Electrical measurements show the breakdown voltage of InP HEMTs increases following exposure to H<sub>2</sub>. The increase in BV<sub>DG</sub> is due to a decrease in the carrier concentration in the extrinsic portion of the device. We provide evidence that H<sub>2</sub> reacts with the exposed InAlAs surface in the extrinsic region of the HEMTs right next to the gate, affecting the underlying carrier concentration. Hall measurements of capped and uncapped HEMT samples show that the decrease in  $n_{s,ext}$  can be attributed to changes in the exposed InAlAs surface. XPS experiments on uncapped heterostructures provide evidence of unrecoverable As loss from the exposed InAlAs surface upon hydrogen exposure.

## ACKNOWLEDGMENT

The authors acknowledge the help of L. Shaw for the XPS measurements. Device fabrication was carried out at the Microsystems Technology Laboratory of MIT.

#### REFERENCES

- R. R. Blanchard, J. A. del Alamo, P. C. Chao, and S. B. Adams, "Hydrogen degradation in InP HEMTs," in *IEDM Tech. Dig.*, 1998, p. 231.

- [2] R. R. Blanchard, J. A. del Alamo, S. B. Adams, P. C. Chao, and A. Cornet, "Hydrogen-induced piezoelectric effects in InP HEMTs," *IEEE Electron Device Lett.*, vol. 20, no. 8, p. 393, Aug. 1999.

- [3] W. O. Camp, R. Lasater, V. Genova, and R. Hume, "Hydrogen effects on reliability of GaAs MMICs," in *Proc. GaAs IC Symp.*, 1989, p. 203.

- [4] W. W. Hu, E. P. Parks, T. H. Yu, P. C. Chao, and A. W. Swanson, "Reliability of GaAs PHEMT under hydrogen containing atmosphere," in *Proc. GaAs IC Symp.*, 1994, p. 247.

- [5] P. C. Chao, M. Y. Kao, K. Nordheden, and A. W. Swanson, "HEMT degradation in hydrogen gas," *IEEE Electron Device Lett.*, vol. 15, no. 5, p. 151, May 1994.

- [6] P. C. Chao, W. Hu, H. DeOrio, A. W. Swanson, W. Hoffmann, and W. Taft, "Ti-gate metal induced PHEMT degradation in hydrogen," *IEEE Electron Device Lett.*, vol. 18, no. 9, p. 441, Sep. 1997.

- [7] R. Gaddi, R. Menozzi, D. Dieci, C. Lanzieri, G. Meneghesso, C. Canali, and E. Zanoni, "Bulk and surface effects of hydrogen treatment on Al/Tigate AlGaAs/GaAs power HFETs," in *Proc. 37th IEEE Annu. Int. Reliability Physics Symp.*, San Diego, CA, 1999, pp. 110–115.

- [8] S. R. Bahl and J. A. del Alamo, "A new drain-current injection technique for the measurement of off-state breakdown voltage in FETs," *IEEE Trans. Electron Devices*, vol. 40, no. 8, p. 1558, Aug. 1993.

- [9] M. H. Somerville and J. A. del Alamo, "A model for tunneling-limited breakdown in high-power HEMTs," in *IEDM Tech. Dig.*, 1996, p. 35.

- [10] Y. L. Chang, R. Cao, W. E. Spicer, P. Pianetta, S. Shi, E. Hu, and J. Merz, "Interaction of hydrogen ions with oxidized GaAs(100) and AlAs(100) surfaces," J. Vac. Sci. Tech.: B, vol. 14, no. 4, p. 2914, 1996.

- [11] W. E. Spicer, N. Newman, C. J. Spindt, Z. Lilental-Weber, and E. R. Weber, ""Pinning" and Fermi-level movement at GaAs surfaces and interfaces," *J. Vac. Sci. Tech.: A*, vol. 8, no. 3, p. 2084, 1990.

- [12] E. S. Aydil, Z. Zhou, K. P. Giapis, Y. Chabal, J. A. Gregus, and R. A. Gottscho, "Real-time, *in situ* monitoring of surface reactions during plasma passivation of GaAs," *Appl. Phys. Lett.*, vol. 62, p. 3156, 1993.

- [13] O. Kubaschewski and C. B. Alcock, *Metallurgical Thermochem*istry. New York: Pergamon Press, 1979.

Jesús A. del Alamo received the degree of Telecommunications Engineer from the Polytechnic University of Madrid, Spain, in 1980, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1983 and 1985, respectively.

From 1977 to 1981, he was with the Institute of Solar Energy of the Polytechnic University of Madrid, working on silicon solar cells. At Stanford University, he carried out his Ph.D. dissertation on minority carrier transport in heavily doped silicon.

From 1985 to 1988, he was a Research Engineer with NTT LSI Laboratories in Atsugi, Japan, where he conducted research on III-V heterostructure field-effect transistors. Since 1988, he has been with the Department of Electrical Engineering and Computer Science of the Massachusetts Institute of Technology (MIT), Cambridge, where he is currently a Professor. His current research interests are on Gigahertz power transistors: Si LDMOS on SOI, RF power CMOS, GaAs PHEMTs, and InP HEMTs. He is also active in online laboratories for science and engineering education.

From 1991 to 1996, Prof. del Alamo was a National Science Foundation Presidential Young Investigator. In 1992, he was awarded the Baker Memorial Award for Excellence in Undergraduate Teaching at MIT. In 1993, he received the H. E. Edgerton Junior Faculty Achievement Award at MIT. In 1999, he was elected a corresponding member of the Royal Spanish Academy of Engineering. In 2001, he received the Louis D. Smullin Award for Excellence in Teaching and the Class of 1960 Innovation in Education Award, both at MIT. In 2002, he received the Amar Bose Award for Excellence in Teaching from MIT. In 2003, he was selected as a MacVicar Faculty Fellow at MIT.

Albert Cornet Calveras was born in 1955. He received the Ph.D. in physics from the University of Barcelona in 1982 and the Ph.D. in sciences from the University Paul Sabatier (Toulouse, France) in 1983.

In 1982 he joined the Department of Applied Physics and Electronics of the University of Barcelona as associate professor, and in 1989 he was appointed full professor of electronics of this Department. His current research activities and projects are centred on the fields of characterization of electronic materials and processes, gas sensors,

semiconductor devices and nanostructured materials. He is author or coauthor of more than 180 scientific and technical papers.

**Roxann R. Blanchard** (M'99) received the B.S. degree in electrical engineering from the University of Vermont, Burlington, in 1989, and the M.S. and Ph.D. degrees in electrical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 1994 and 1999, respectively. Her Ph.D. work included the study and fabrication of InP-channel and InGaAs-channel InP HEMTs. In addition, she examined the effects of hydrogen exposure on InGaAs/InAlAs HEMTs and GaAs PHEMTs.

From 1989 to 1994, she worked at Raytheon Company, Sudbury, MA, developing radiation-hardened CMOS and BiCMOS processes. Since 1999, she has been with Advanced Linear Products at Analog Devices Inc., Wilmington, MA, working on analog/RF circuit design.