# Analytical Model for RF Power Performance of Deeply Scaled CMOS Devices

<u>Usha Gogineni<sup>1</sup></u>, Jesús del Alamo<sup>1</sup>, Alberto Valdes-Garcia<sup>2</sup>

<sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA <sup>2</sup>IBM T.J. Watson Research Center, Yorktown Heights, NY

RFIC – Baltimore 5-7 June 2011

# Outline

- Motivation

- Technology and Measurement Details

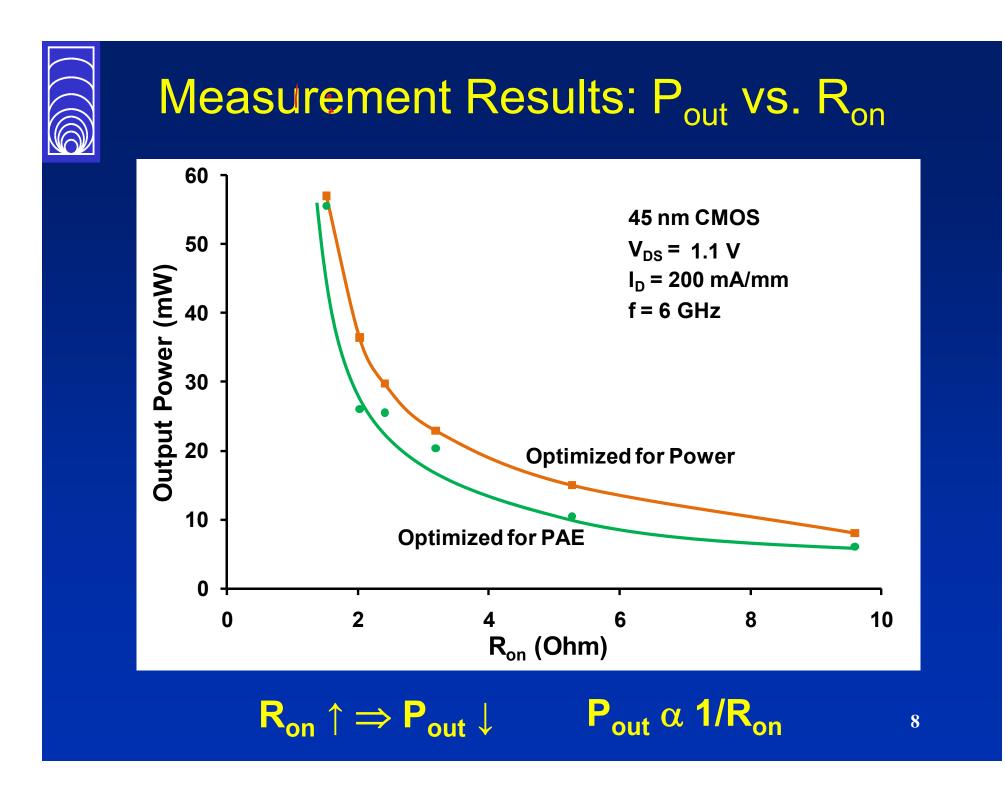

- Effect of R<sub>on</sub> on Maximum P<sub>out</sub>

- Analytical Model Description

- Comparison of Model with Measurements

- Conclusions

# **Motivation**

### Poutmax often estimated through RF power simulations

- Time consuming

- Need accurate compact models

- CMOS models usually tailored for digital applications

#### Need an analytical model that can

- Provide physical understanding of basics of power scaling

- Estimate power capability of a device without need for complex models or simulations

# **Pros & Cons of Analytical Model**

#### **Pros:**

- Predicts P<sub>outmax</sub> and trade-off between P<sub>out</sub> and PAE

- Correctly accounts for R<sub>on</sub> of the device

- No need for complex models or simulations

#### Limitations:

Frequency dependence is ignored

(for 2-18 GHz, the measured P<sub>out</sub> is independent of f)

# Technology & Measurement Details

#### Technology:

- 45 nm Low Power CMOS Technology from IBM

- $V_{DD}$  = 1.1 V, Gate Length = 40 nm

- Total Gate Width = 40  $\mu$ m to 640  $\mu$ m

- W  $\uparrow$  using multiple unit cells (WF = 2  $\mu$ m, NF = 20)

#### Measurements:

- Load-pull measurements using Maury Microwave system

- Frequency = 2 18 GHz

- $V_{DS}$  = 1.1V,  $V_{GS}$  set to ensure  $I_D$  = 200 mA/mm

- Source and load impedances tuned for (a) max.  $\mathsf{P}_{\mathsf{out}}$  and (b) max. PAE

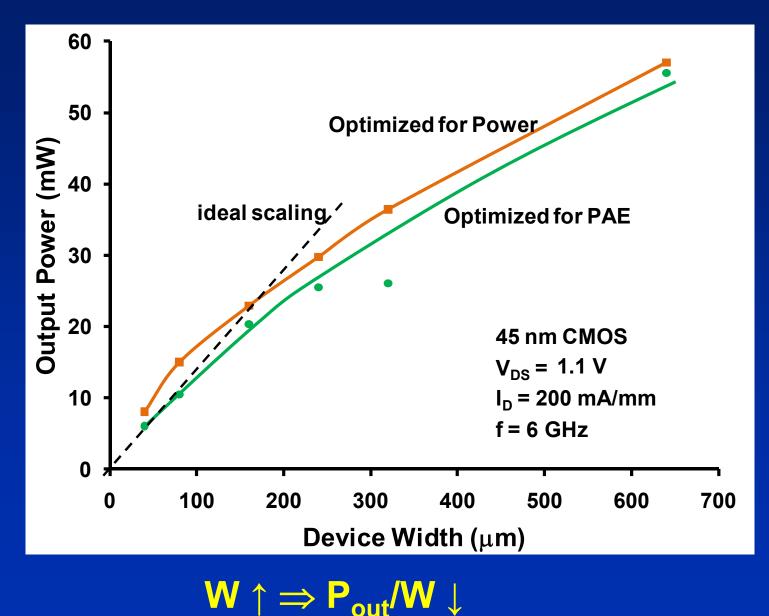

# Measurement Results: Pout vs. W

6

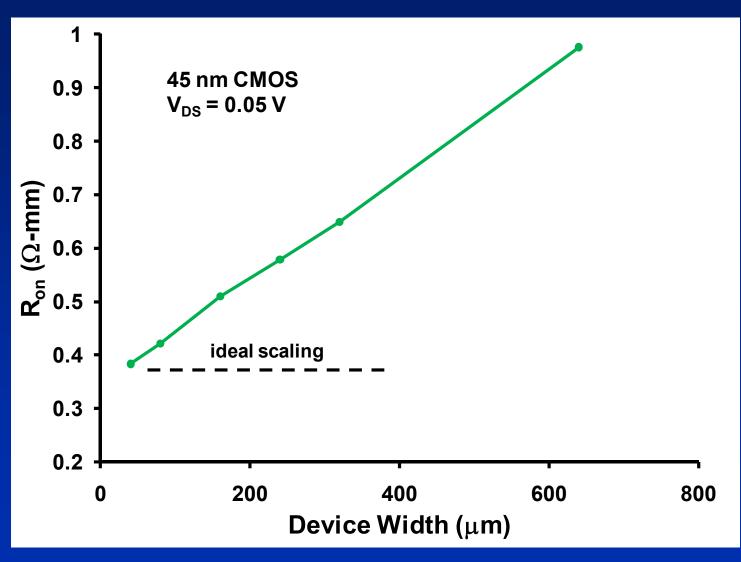

## Measurement Results: R<sub>on</sub> vs. W

R<sub>on</sub> does not scale ideally with width

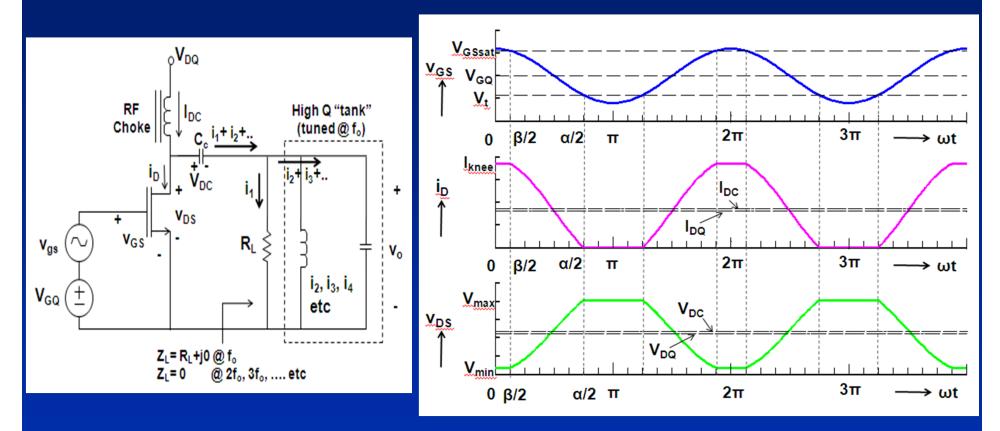

## **Model Description**

Ref: Cripps, RF power amplifiers for wireless communications, 2006

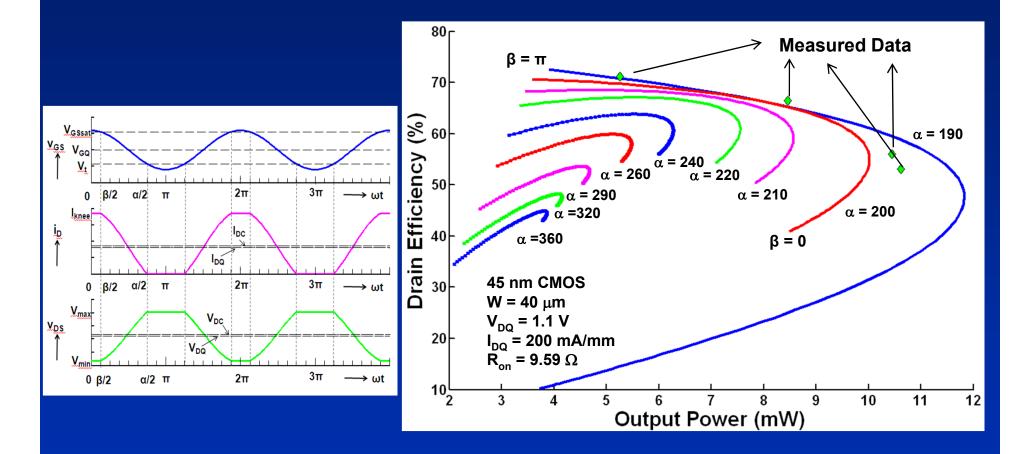

# **Model Equations**

$$i_{D}(\omega t) = \begin{cases} I_{knee} & -\frac{\beta}{2} \le \omega t \le \frac{\beta}{2} \\ I_{DQ} \left( 1 - \frac{\cos \omega t}{\cos \frac{\alpha}{2}} \right) & \frac{\beta}{2} \le |\omega t| \le \frac{\alpha}{2} \\ 0 & \frac{\alpha}{2} \le |\omega t| \le \pi \end{cases}$$

$$I_{DC} = \frac{1}{2\pi} \int_{-\pi}^{\pi} i_D(\omega t) d(\omega t)$$

$$I_1 = \frac{1}{\pi} \int_{-\pi} i_D(\omega t) \cos \omega t \, d(\omega t)$$

$$v_{DS}(\omega t) = \begin{cases} V_{min} & 0 \le |\omega t| \le \frac{\beta}{2} \\ \frac{V_{min} \cos \frac{\alpha}{2} - V_{max} \cos \frac{\beta}{2}}{\cos \frac{\alpha}{2} - \cos \frac{\beta}{2}} + \frac{(V_{max} - V_{min}) \cos \omega t}{\cos \frac{\alpha}{2} - \cos \frac{\beta}{2}} & \frac{\beta}{2} \le |\omega t| \le \frac{\alpha}{2} \\ V_{max} & \frac{\alpha}{2} \le |\omega t| \le \pi \end{cases} \quad V_{DC} = \frac{1}{2\pi} \int_{-\pi}^{\pi} v_{DS}(\omega t) d(\omega t) \\ V_{1} = \frac{1}{\pi} \int_{-\pi}^{\pi} v_{DS}(\omega t) \cos \omega t d(\omega t) \end{cases}$$

$$P_{DC} = V_{DQ} \cdot I_{DC}$$

$P_{out} = \frac{I_1}{\sqrt{2}} \cdot \frac{V_1}{\sqrt{2}}$

$$\eta_D (\%) = \frac{P_{out} * 100}{P_{DC}}$$

$$R_L = \frac{V_{max} - V_{min}}{I_{knee}}$$

10

## Modeled Power-Efficiency Locus

$P_{out}$  -  $\eta_D$  locus can be generated for any given  $V_{DQ}$ ,  $I_{DQ}$ ,  $R_{on}$

## Model Usage

- Model generates  $\textbf{P}_{\text{out}}$   $\eta_{\text{D}}$  locus at any operating point

- Need to choose either  $\textbf{P}_{\text{out}}$  or  $\eta_{\text{D}}$  to determine the other

- No adjustable parameters in model

| Inputs          | Intermediate | Outputs          |

|-----------------|--------------|------------------|

| V <sub>DQ</sub> |              | P <sub>out</sub> |

| I <sub>DQ</sub> | α            | _                |

| R <sub>on</sub> | β            | I <sub>DC</sub>  |

| $\eta_{D}$      |              | R <sub>L</sub>   |

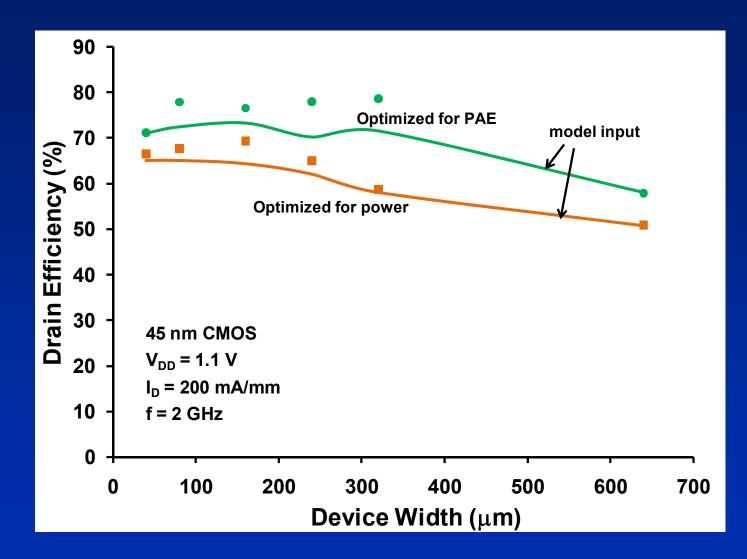

# Modeled Drain Efficiency vs. W

#### $\eta_{D}$ for model input chosen close to measured values

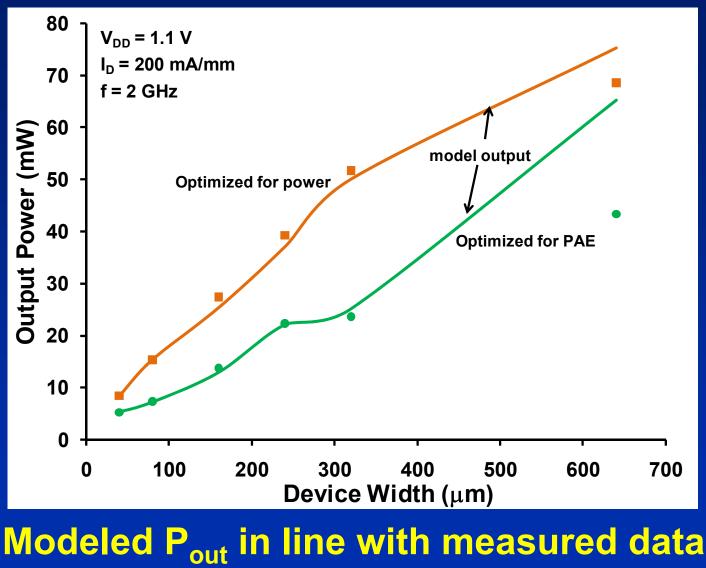

# Modeled P<sub>out</sub> vs. W

except for large  $W \rightarrow Self heating?$

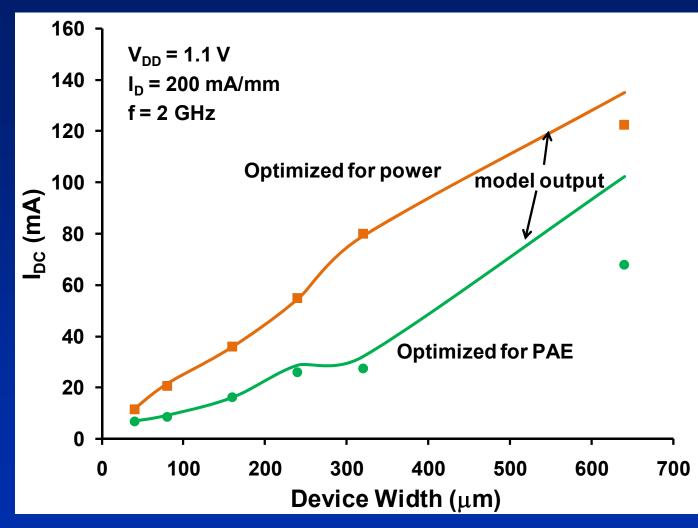

## Modeled Average I<sub>D</sub> vs. W

Good agreement between I<sub>DCmeas</sub> and I<sub>DCmodel</sub> except for large W Decrease in measured I<sub>DC</sub> and P<sub>out</sub> at large W due to self heating

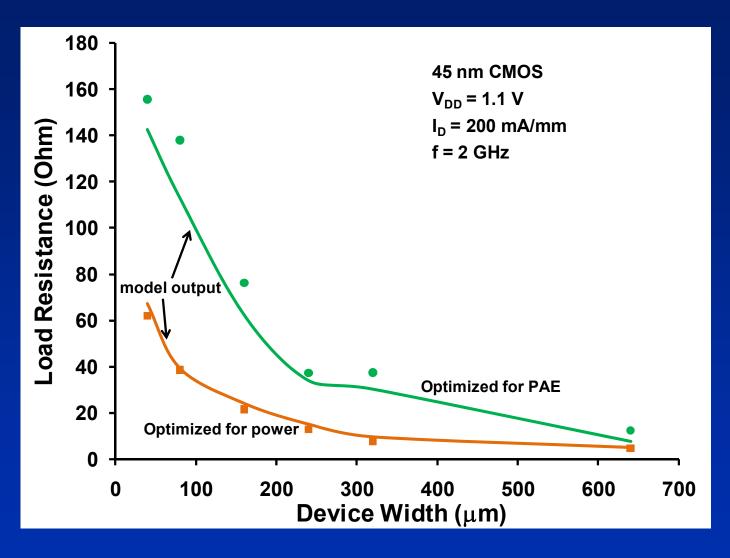

# Modeled R<sub>L</sub> vs. W

#### Modeled R<sub>L</sub> very close to measured values

## Conclusions

Simple analytical model allows quick calculations of maximum  $P_{out}$  and  $\eta_D$  for any CMOS device - Inputs: DC operating point and R<sub>on</sub> - Outputs:  $P_{outmax}$  and  $R_L$  at any given  $\eta_D$  Excellent agreement with measured data (45 nm) •  $R_{D}$ ,  $R_{S}$  extracted from layout (parasitic extractions)  $\rightarrow$  Model can estimate P<sub>outmax</sub> for any layout R<sub>on</sub> most significant limiter to P<sub>out</sub> in CMOS

## Acknowledgements

- Semiconductor Research Corporation (Grant 2007-HJ-1661)

- IBM Microelectronics for fabricating test structures