# Fabrication and Characterization of Through-Substrate Interconnects

Joyce H. Wu and Jesús A. del Alamo, Fellow, IEEE

Abstract—We developed a through-substrate copper-damascene interconnect technology in silicon with minimal impedance. Via impedance was extracted using S parameter measurements at 50 GHz that were matched to simple circuit models. The extracted impedance shows resistances  $\leq 1~\Omega$ , record-low inductance for aspect ratios > 4, and sidewall capacitance that approaches the theoretical value. For an aspect ratio of 10 (10  $\mu$ m in diameter and 100  $\mu$ m high), the through-substrate via has an average inductance of 36 pH at 10 GHz, resistance of 0.6  $\Omega$  at 1 GHz, and sidewall capacitance of 0.3 pF.

Index Terms—Ground inductance, Si RF technology, substrate crosstalk, substrate via, through-substrate via, through-wafer interconnect, through-wafer via, via inductance.

#### I. Introduction

THROUGH-SUBSTRATE interconnects of high-aspect ratio and with low parasitic impedance can find many applications in various semiconductor fields. Specifically, through-wafer interconnects can alleviate interconnect scaling issues in digital circuits, power and ground inductance in silicon radio frequency integrated circuits (RFICs), substrate noise in mixed-signal circuits, and packaging size and cost in microelectromechanical systems (MEMS) and system-in-package (SiP) applications.

Integration and scaling have been the fundamental goals of the semiconductor industry to reduce cost and boost performance. As devices have scaled according to Moore's law, interconnects have lagged. While circuit performance improves as devices scale, interconnect scaling results in longer latency and higher power consumption. Interconnects have quickly become the bottleneck in circuit performance, and managing the need for ever-higher transmission speeds with further scaling is the primary concern for interconnects. Currently, interconnects are laid out on the surface of the chip in an increasing number of metal levels (12 layers at present [1]) and just barely meet performance needs. In addition, continuing integration of circuit functionality onto one chip has been stimulated by the wireless industry for better portability and lower power consumption.

Manuscript received November 24, 2009; revised February 17, 2010; accepted February 18, 2010. Date of publication April 22, 2010; date of current version May 19, 2010. This work was supported in part by the Applied Materials Graduate Fellowship. The review of this paper was arranged by Editor M. J. Kumar.

- J. H. Wu was with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA. She is now with Pixtronix, Inc., Andover, MA 01810 USA (e-mail: jowu@mit.edu).

- J. A. del Alamo is with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: alamo@mit.edu).

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2010.2045671

This has increased the complexity of not only circuit design but also the demands on interconnects. As metal line widths shrink and line lengths increase, parasitic resistance, capacitance, and inductance degrade circuit performance by increasing delays, loading, and power consumption [2]. Particularly, interconnect inductance contributes to power and ground bounce. Through-substrate vias can help alleviate these problems by reducing line length and minimizing parasitic impedance, especially inductance.

Consumer RF systems have traditionally been fabricated using III–V materials that use through-substrate vias to reduce ground inductance. Silicon has rapidly been supplanting III–Vs because of its lower manufacturing costs and its integration capabilities [3]. Improving the high-frequency performance of silicon by reducing ground inductance with through-substrate vias will project silicon technology into high-end RF and millimeter-wave applications. Furthermore, silicon-based systems allow for integration with digital blocks for system-on-chip (SoC). However, this introduces digital noise into the substrate, which interferes with the operation of RF/analog circuits. This can be mitigated using through-substrate vias wired into a Faraday cage that can suppress crosstalk between blocks [4].

Separately, MEMS packages typically exceed the cost of the device and impose severe design constraints [5]. Introducing low-impedance through-substrate vias as a backside interconnect would reduce packaging size and cost [5]. Through-substrate vias could also provide an interlevel interconnect for MEMS constructed from several bonded wafers.

Through-substrate interconnects also reduce parasitics in packaging, specifically SiP designs [1], by decreasing line length and increasing packing density. This includes multi-layer silicon die and chip stacks without parasitic wire bonds and ultimately extends to wafer-level packaging [1], [2], [6], [7]. These examples of SiP can offer the integration of passives, memory, MEMS, RF subsystems, and digital blocks of great interest for wireless applications [1].

To address these applications (Fig. 1), we have developed a through-substrate interconnect technology in silicon using a copper damascene process that allows for ground, power, and signals to be distributed from the backside using high-aspectratio low-impedance vias. This paper builds upon previous work on ground vias (single node) [8] but with a completely new process. This new work features backside patterning that allows for backside power, ground, and signal distribution on the same chip. Vias are now completely isolated from the silicon substrate, which was not accomplished using the previous process.

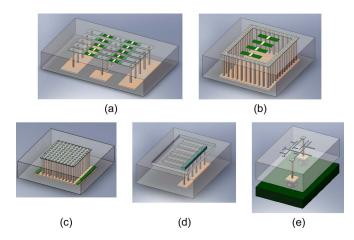

Fig. 1. Various applications of through-substrate interconnects in silicon. (a) Backside interconnect for power, ground, and signals. (b) Faraday cage for substrate noise isolation for SoC. (c) Integrated capacitors. (d) Backside contact for MEMS. (e) Backside package mount for SiP.

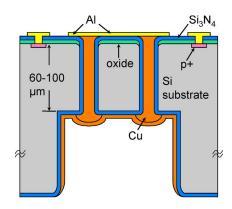

Fig. 2. Cross-sectional illustration of through-substrate vias.

This paper represents an augmented version of a preliminary conference presentation of this work [4].

#### II. FABRICATION

The through-substrate vias were fabricated on n- and p-type wafers (0.01–10  $\Omega \cdot \mathrm{cm}$ ). Wafers were locally thinned to 60–100  $\mu\mathrm{m}$  in backside trenches to emulate thin substrates without having to deal with them in this demonstration study. The vias in the same backside trench were connected to each other but not to vias in other trenches, so that power, ground, and signals could be routed on the backside of the same chip. Fig. 2 depicts a cross section of a completed through-substrate via.

## A. Process Flow

The fabrication of through-substrate vias required the development and thorough characterization of new process steps before integrating into one complete process. The major process steps flow as follows: patterning the substrate backside, etching of the through-substrate via from the front, depositing a conformal dielectric liner, filling the via with electroplated copper, and removing excess copper by chemical–mechanical polishing

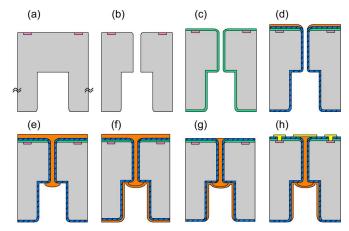

Fig. 3. Through-substrate via process flow. (a) Boron implant on the frontside and backside trenches etched by DRIE. (b) Through-substrate vias etched from frontside by DRIE. (c) Via sidewalls smoothed by growing and stripping oxide. (d) Oxide deposited on frontside, conformal silicon nitride liner deposited, and Ti-Cu seed deposited on frontside. (e) Via filled with Cu by electroplating. (f) Cu sputtered onto backside. (g) Cu removed from front and back of substrate by CMP. (h) Contact holes etched and Al pads deposited, patterned, and etched.

(CMP). Improvements over previous work [8] and changes in the via process to accommodate backside patterning and new test structures include a deep reactive-ion etch (DRIE) for backside thinning, sidewall smoothing, a conformal silicon nitride liner, efficient copper electroplating, copper CMP, and the introduction of ohmic contacts to the substrate. These new steps are also an improvement over the via processes in [9]–[11].

Fig. 3 describes the through-substrate via process. First, boron is implanted for ohmic contacts using thermal oxide and resist as a mask [Fig. 3(a)]. To thin the wafers down to 60-100  $\mu$ m, trenches were etched from the backside of the wafer using an anisotropic DRIE [Fig. 3(a)]. DRIE etches nearly vertical sidewalls so that the trenches had a much smaller footprint than when using a KOH etch [12], [13]. The throughsubstrate vias were also etched from the frontside by DRIE using resist and deposited oxide as a mask [Fig. 3(b)]. This was a through etch, so a handle wafer was needed to prevent etch gases from passing into the helium-cooled chuck. Because DRIE produces rough sidewalls, a thermal oxide was grown and then stripped to leave a smooth sidewall surface for the liner [Fig. 3(c)]. A 2000-Å oxide was then deposited on the frontside as an etchstop for contacts etched later in the process [Fig. 3(d)]. A conformal silicon nitride liner was deposited to protect the silicon substrate from copper diffusion from the copper core of the via [Fig. 3(d)]. Silicon nitride also electrically insulated the substrate from the via so signals could be routed through the substrate. More details are given in the next section.

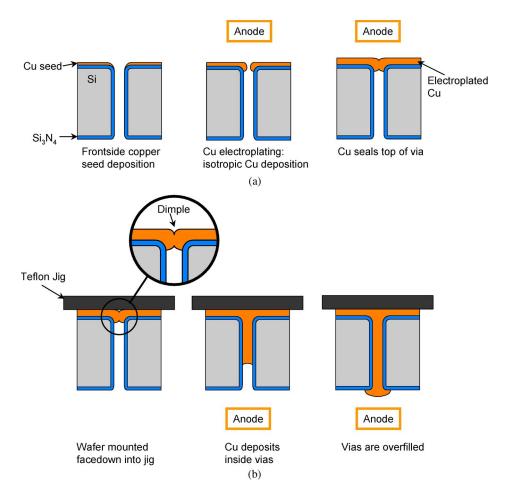

Proceeding with metallization, a Ti-Cu seed was deposited on the frontside to facilitate copper electroplating that filled the via [Fig. 3(d)]. Due to the isotropic deposition of electroplating, the top of the via closed first and then filled from top to bottom [Fig. 3(e)]. Electroplating was stopped when copper protruded from the via into the backside trench. Next, copper was sputtered on the back and fully coated the inside of the DRIE trenches so that all the vias in one trench are connected to each another [Fig. 3(f)]. This provided a local connection

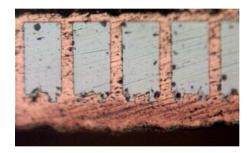

Fig. 4. Picture of vias (before CMP) 13  $\mu{\rm m}$  in diameter and 100  $\mu{\rm m}$  high ( AR=8 ).

for all the vias in the trench. The sputtered backside copper was removed by CMP to isolate each trench from one another while keeping the copper inside the trench intact [Fig. 3(g)]. The frontside copper was also removed using CMP to complete the copper damascene process [Fig. 3(g)]. More details are given below. Contact openings to the substrate were then etched through the silicon nitride and silicon dioxide films on the front surface [Fig. 3(h)]. Finally, aluminum was e-beam deposited, annealed, and patterned to form test structures [Fig. 3(h)]. The measured via diameters varied from 2 to 30  $\mu$ m. The substrate thicknesses ranged from 60 to 100  $\mu$ m. Fig. 4 shows a cross section of vias 13  $\mu$ m in diameter and 100  $\mu$ m high.

This demonstration project was fabricated to evaluate the electrical characteristics of through-substrate vias and not to propose a specific approach for manufacturing. The high-temperature steps, such as the thermal oxidation for sidewall smoothing and low-pressure chemical vapor deposition (LPCVD) silicon nitride, were chosen from the limited toolset available, and these steps would need alteration if this process was to be used in the back-end. More details of specific process steps are given next.

#### B. Silicon Nitride Liner

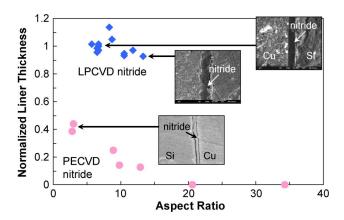

We used silicon nitride as the via liner material because of its barrier properties to copper diffusion and to electrically isolate the via from the silicon substrate [14]–[16]. Silicon nitride was deposited using LPCVD because of its higher conformality over plasma-enhanced chemical vapor deposition (PECVD). Fig. 5 shows measurements of PECVD and LPCVD silicon nitride thickness on the via sidewall divided by the surface thickness and plotted against via aspect ratio. The sidewall thickness measurement was taken halfway down the via at the thinnest point of the liner. The LPCVD nitride thickness is nearly constant all the way down the via, while PECVD nitride is minimal for aspect ratios higher than 15 [8].

# C. Copper Electroplating

The low resistivity of copper allows for high current densities in interconnects, and copper has been proven to have increased scalability and better electromigration reliability than Al(Cu) interconnects [17]. Some of the disadvantages of copper are its poor adhesion to dielectrics and the need for barrier and/or adhesion layers [17]. However, copper has the critical advantage of being able to fill high-aspect-ratio holes by electroplating.

Fig. 5. Silicon nitride sidewall thickness normalized to surface thickness versus actual aspect ratio for PECVD nitride from previous work [8] and LPCVD nitride. The sidewall thickness was taken halfway down the via at the thinnest point of the liner.

We used a commercial copper sulfate solution from Enthone-OMI and a Dynatronix DuPR 10-1-3 current supply with pulse-reverse current, which enhances electrodeposition into high-aspect-ratio structures. The dissolution of copper during the negative pulse provides a better concentration gradient of cupric ions in the via than a dc pulse, so that during the subsequent positive pulse, the deposition is more uniform and the void size is reduced [18]-[20]. After depositing a seed of 250 Å of titanium and 2000 Å of copper on the frontside of the wafer, the wafer was placed into the copper electroplating solution with the seed facing the anode. An average current density of 4.6 mA/cm<sup>2</sup> was applied. This blanket plating step produced an isotropic deposition of copper on the seed until the via closed at the top, as depicted in Fig. 6(a), similar to [8] and [9]. Due to the nonuniformity of the deposition, the wafer was rotated 180° halfway through the deposition. The cause for the nonuniformity is possibly due to a gradient of copper ions in the bath such that the deposition is greater at deeper levels in the bath. A faster stirring speed would enhance mixing but also increases the dissolved oxygen in the bath. Once most vias had closed, which was after about 75 min, the wafer was removed from the bath. The deposition rate was approximately  $0.15 \mu m/min.$

In the second step, the wafer was placed facedown into a Teflon jig so that the frontside would not be exposed to the copper solution [Fig. 6(b)]. The jig prevented excess copper from being electroplated onto the frontside so that less copper would have to be removed during CMP in a later stage. In addition, isolating the frontside seed from the solution significantly reduced the surface area to be plated so that a higher current density could be applied. The exposed area was actually too small because only a small amount of copper inside the vias was exposed to the solution. Therefore, two 22-cm<sup>2</sup> dummy pieces electrically connected to the cathode (wafer) were also placed into the solution on either side of the jig. An average pulse-reverse current of 12.5 mA/cm<sup>2</sup> was applied until all the vias were filled. The wafer was rotated 180° halfway through the deposition because of the nonuniformity of the plating bath, and then the vias were overfilled. Because the plated copper of the first plating step must traverse the opening to close the via,

Fig. 6. Copper electroplating steps to reduce deposition time and excess copper buildup on the seed. (a) Blanket plating step. (b) Electroplating with wafer inserted into jig.

larger-diameter vias take longer to close and thus take longer to fill. To ensure that all the vias are filled with copper, the smaller-diameter vias become overfilled into the backside trenches. The deposition rate averaged around 1  $\mu$ m/min. Using the jig, the amount of excess copper plated onto the seed reduced to 10–20  $\mu$ m from 40  $\mu$ m in our earlier process [8].

# III. MEASUREMENT

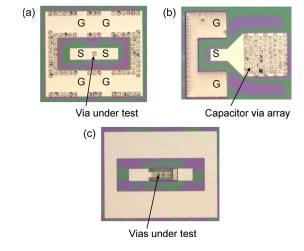

We characterized the through-substrate vias by measuring the S parameters from 0.1 to 50 GHz of various coplanar ground–signal–ground RF test structures pictured in Fig. 7. The via impedance was extracted from  $S_{21}$  measurements of the two-port test structure in Fig. 7(a). The via under test lies in the center of the signal line and connects to a local ground plane inside the backside DRIE trench. This copper backplane lines the backside DRIE trench, which extends to the edge of the aluminum ground pads. The ground lines are punctuated by many vias to reduce the impedance from the copper backplane to the ground pads. The ground vias are  $10~\mu m$  in diameter.

The sidewall capacitance of the via to the substrate was measured using one-port test structures like that in Fig. 7(b) on p<sup>+</sup> wafers (< 0.03  $\Omega$  · cm or less). To minimize the impact of pad capacitance, the test structures consist of arrays of 77 or 431 vias in parallel.

Fig. 7. Pictures of coplanar ground–signal–ground RF test structures. (a) Two-port impedance. (b) One-port capacitance: the signal is connected to the 77-via array, and the ground is the p<sup>+</sup> implant. (c) Leakage test structure.

The integrity of the liner was evaluated by measuring the current leakage across the silicon nitride liner using the test structure in Fig. 7(c). The left pad is connected to the top of the copper vias, which are arranged in arrays of one to four vias in parallel. The right pad is connected to the silicon surrounding the vias through an ohmic contact to the substrate. The via

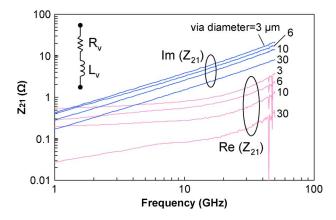

Fig. 8.  $Z_{21}$  (converted from  $S_{21}$ ) versus frequency for vias of diameter 3, 6, 10, and 30  $\mu$ m. The real part represents resistance and rises at high frequency due to the skin effect. The imaginary part increases with a slope of 1, indicating inductive behavior.

diameter was varied from 2 to 10  $\mu$ m. The current leakage across the larger via arrays in Fig. 7(b) was also measured.

The through-substrate vias were measured using  $125-\mu\mathrm{m}$  pitch GGB Industries Inc. microwave probes. The probes were connected to an HP8510C network analyzer for S parameter measurements up to 50 GHz. The power was set to 10 dBm and 0-dB attenuation. For the two-port impedance test structure,  $S_{21}$  was measured from 100 MHz to 50 GHz. For the one-port capacitance test structure,  $S_{11}$  was measured up to 50 GHz. The measured S parameter data were converted to S parameters for analysis. The leakage current was measured on the same probe station but using dc probes and an HP4155. The wafer chuck was grounded to the HP4155 in all the measurements.

Additional test structures were also fabricated to test the substrate crosstalk isolation properties of several Faraday cage designs [4]. A full report on these findings is forthcoming.

# IV. RESULTS AND DISCUSSION

From the converted Z parameter data, we extracted the inductance, resistance, and sidewall capacitance of a single via. Simple circuit models and theoretical calculations are used to explain these results.

## A. Via Inductance and Resistance

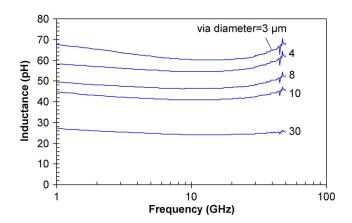

$Z_{21}$  measurements of the impedance test structure in Fig. 7(a) are plotted in Fig. 8 for different via diameters. Looking at the real and imaginary parts of  $Z_{21}$ , a through-substrate via can be represented by a simple circuit model of a resistor and an inductor in series. The real part represents the via resistance  $R_v$ , and the imaginary part  $\omega L_v$  linearly rises with frequency and represents the susceptance, which is associated with inductance. From this circuit model, the resistance and inductance of a single via can be extracted. Fig. 9 plots the inductance  $L_v$  against frequency.

As shown in Fig. 8, although the real part should remain constant, it rises with frequency due to the skin effect. At high frequencies, the resistance increases as current crowds to the sidewalls of the via. Current travels along the copper via

Fig. 9. Inductance  $L_v$  versus frequency for vias of diameter 3, 4, 8, 10, and 30  $\mu m$

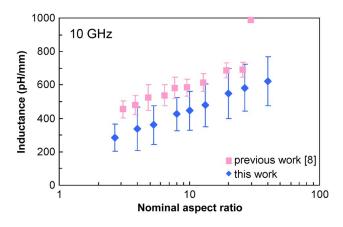

Fig. 10. Via inductance per unit length versus nominal aspect ratio of a via at 10 GHz. The via diameters ranged from 2 to 30  $\mu$ m. The via height ranged from 60 to 100  $\mu$ m, so an average of 80  $\mu$ m was used for aspect ratio. The measured inductance data (blue diamonds) falls below previous work [8] (pink squares) by using a two-port test structure and improved process.

sidewall down to the skin depth. At 1 GHz, the skin depth in copper is 2.1  $\mu$ m and decreases to 0.3  $\mu$ m at 50 GHz. This is thin enough to affect the resistance and inductance in even the smallest diameter via.

The inductance at 10 GHz was extracted from data in Fig. 9 and other measurements and is plotted in Fig. 10 (blue diamonds) against nominal aspect ratio. The inductance falls significantly below our previous work [8] (pink squares). We attribute this to the reduced parasitics of the new two-port test structure and a superior process. Previous work fabricated vias using a PECVD nitride that was not completely conformal, and the measurements used a one-port test structure. The new results shown in Fig. 10 represent the lowest inductance reported for high-aspect-ratio (> 4) through-substrate vias [10], [11].

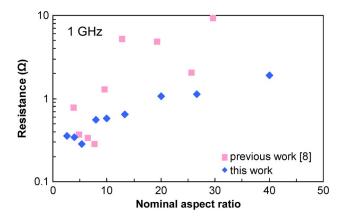

The extracted resistance was taken at 1 GHz to minimize the effects of skin depth and is plotted in Fig. 11 (blue diamonds) against nominal aspect ratio. The resistance is approximately 1  $\Omega$  or less and decreases with via diameter. The resistance data from previous work [8] are also plotted in Fig. 11. The new via measurements showed a significant drop in resistance compared with previous work [8] with less scatter. This is likely due to the lower parasitics of the two-port structure. There is a discrepancy between the extracted resistance and the theoretical

Fig. 11. Via resistance versus nominal aspect ratio of a via at 1 GHz. Via diameters ranged from 2 to 30  $\mu$ m, and via height was averaged to 80  $\mu$ m. The measured data (blue diamonds) have lower resistance than previous work [8] (pink squares) by using a two-port test structure.

resistance, which can be attributed to parasitics of the two-port test structure and contact resistance. De-embedding structures were not fabricated for this test structure.

# B. Sidewall Capacitance

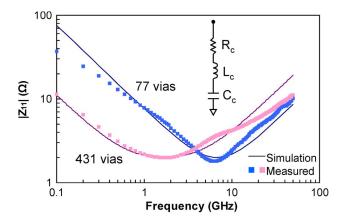

The sidewall capacitance of the via to the substrate was measured using the one-port test structure in Fig. 7(b) on p<sup>+</sup> wafers. To minimize the impact of pad capacitance, the test structure consists of arrays of 77 or 431 vias in parallel. The vias are nominally 10  $\mu$ m in diameter and spaced by 10  $\mu$ m. Fig. 12 plots  $|Z_{11}|$  against frequency for each array size. We find that  $|Z_{11}|$  follows a simple model of a capacitor, resistor, and inductor in series, for which

$$Z_{11} = R_c + j \left( \frac{\omega^2 L_c C_c + 1}{\omega C_c} \right) \tag{1}$$

where  $R_c$  is the total resistance of the via array,  $L_c$  is the total inductance of the via array, and  $C_c$  is the total capacitance of the via array test structure. The resonant frequency is

$$\omega_0 = \sqrt{\frac{1}{L_c C_c}} \tag{2}$$

which occurs at the minimum  $|Z_{11}|$ , as shown in Fig. 12. At frequencies below the resonant frequency,  $C_c$  dominates so that

$$|Z_{11}| \simeq \frac{1}{\omega C_c} \tag{3}$$

and so the sidewall capacitance was extracted at these frequencies. To verify this circuit model, we simulated it with Agilent ADS software using the extracted resistor, capacitor, and inductor values. The simulations closely match the measured data, as shown in Fig. 12. The mismatch at high frequencies is due to the skin effect.

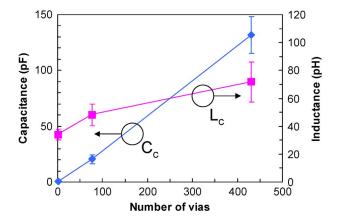

The average extracted capacitance and inductance of the via arrays are plotted in Fig. 13. For the 77-via array, the average capacitance was 20 pF, and for the 431-via array, the average capacitance was 132 pF. The single-via data points were obtained from average measurements of the test structure in Fig. 7(a). Taking the slope of the capacitance line, we get a

Fig. 12.  $|Z_{11}|$  versus frequency for via arrays of 77 and 431 vias measured using the capacitance test structure in Fig. 7(b). The vias are approximately 95  $\mu$ m tall and nominally 10  $\mu$ m in diameter. This structure can be represented by a capacitor in series with a resistor and inductor. Simulations of this model are plotted in the solid line for each via array. The via sidewall capacitance was extracted from this model.

Fig. 13. Extracted capacitance and inductance from measurements of Fig. 7(b). The width of the error bars is one standard deviation. The capacitance is roughly linear with the number of vias. The inductance increases with the number of vias due to mutual inductance.

capacitance of 0.31 pF for an individual via. This approaches the theoretical capacitance of 0.33 pF for a 10- $\mu$ m-diameter 100- $\mu$ m-high via with a 7000-Å silicon nitride liner. Nearly perfect scaling of capacitance with the number of vias is shown in Fig. 13. Using vias with a 1:1 pitch for high-density integrated capacitors, the expected capacitance per footprint area is about 0.1  $\mu$ F/cm<sup>2</sup>, similar to thin-film capacitors. By increasing the aspect ratio to our processing limit of 50, 0.4  $\mu$ F/cm<sup>2</sup> can be reached. By decreasing the silicon nitride thickness from 700 to 100 nm, an even greater capacitance of 2.7  $\mu$ F/cm<sup>2</sup> is attainable. A higher capacitance density will require a dielectric with a higher dielectric constant. This is promising for via applications such as decoupling capacitors and integrated capacitors.

The through-substrate vias in the large via arrays in the capacitance test structure [Fig. 7(b)] are connected in parallel. An interesting finding in this structure is that the total extracted inductance actually increases as more vias are placed in parallel, as shown in Fig. 13. This is due to the mutual inductance of the via array. (The resistance changes little because it is swamped by the parasitic resistance of the one-port test structure.) With more vias in parallel, the self-inductance decreases, but the

Fig. 14. Current leakage versus applied voltage across four vias in parallel for different via diameters (2–10  $\mu$ m) and for 77- and 431-via arrays. The via diameter is 10  $\mu$ m for the via arrays. The leakage for the open test structure is indicated by a thick black line.

mutual inductance increases faster, so that the total inductance goes up. This is an important consideration when using these vias in high-frequency circuits.

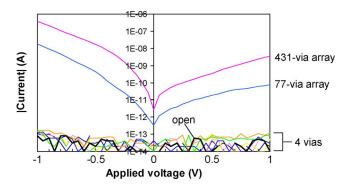

### C. Liner Integrity

We tested the integrity of the LPCVD silicon nitride liner by measuring the current leakage through the via sidewall using the test structures in Fig. 7(b) and (c) on p<sup>+</sup> wafers. Fig. 14 plots the measured current across the liner of several test structures against an applied voltage of -1 to 1 V. In the four-via structure [Fig. 7(c)], the leakage was measured from the copper via to the silicon substrate for via diameters of 2 to 10  $\mu$ m. In all cases, the current leakage is in the sub-pA range and lies within the same current range as the open test structure. These currents are below the noise floor of the measurement setup. However, measurements of the larger via arrays in Fig. 7(b) showed that some vias were actually shorted to the substrate. The via arrays that were not shorted had current leakage less than 1  $\mu A$  for the 431-via array and sub-pA to 100-nA range for the 77-via array. Fig. 14 shows measurements of each size via array that was not shorted.

It is not entirely clear if the shorts were due to defects in the liner in the via sidewall or at the top surface. It is likely that during the nitride etch step, the photoresist was thinner around the edges of the via in the via arrays due to the uneven coating over the vias. The unprotected silicon nitride was etched, revealing the silicon substrate. In addition, the nitride was already thinner at this step due to CMP.

# V. CONCLUSION

We have developed a versatile through-substrate interconnect technology with minimal impedance that allows for backside routing of power, ground, and signals for 3-D and SiP integration, low-ground inductance for RFICs, substrate noise isolation for mixed-signal circuits, and a backside contact for MEMS.

S parameter measurements of the through-substrate vias show that the copper via can be represented by a simple equivalent circuit of a resistor and inductor in series, from which the via resistance and inductance were extracted. The

resistance was less than 1  $\Omega$  and decreased with via diameter. The via inductance was the lowest ever reported for vias of aspect ratio greater than 4. Using via arrays, the extracted via sidewall capacitance matched the theoretical capacitance calculations of a single via 10- $\mu$ m diameter and 100  $\mu$ m high. Fully characterizing the through-substrate vias provides the basis for vias to be incorporated in circuits and other applications.

#### ACKNOWLEDGMENT

The authors would like to thank K. Jenkins of IBM for his advice in designing the test structures. All fabrication was performed at the MIT Microsystems Technology Laboratories.

### REFERENCES

- [1] International Technology Roadmap for Semiconductors, 2007.

- [2] K. Banerjee, S. J. Souri, P. Kapur, and K. C. Saraswat, "3-D ICs: A novel chip design for improving deep-submicrometer interconnect performance and systems-on-a-chip integration," *Proc. IEEE*, vol. 89, no. 5, pp. 602– 633, May 2001.

- [3] A. Matsuzawa, "RF-SoC—Expectations and required conditions," IEEE Trans. Microw. Theory Tech., vol. 50, no. 1, pp. 245–253, Jan. 2002.

- [4] J. H. Wu and J. A. del Alamo, "Through-substrate interconnects for 3-D ICs, RF systems, and MEMS," in *Proc. IEEE Topical Meeting Silicon Monolithic ICs RF Syst.*, 2007, pp. 154–157.

- [5] S. J. Ok, "High density, high aspect ratio through-wafer electrical interconnect vias for MEMS packaging," *IEEE Trans. Adv. Packag.*, vol. 26, no. 3, pp. 302–309, Aug. 2003.

- [6] S. Savastiouk, O. Siniaguine, J. Reche, and E. Korczynski, "Thru-silicon interconnect technology," in *Proc. IEEE CPMT Int. Electron. Manuf. Technol. Symp.*, 2000, pp. 122–128.

- [7] K. Takahashi, K. Tanida, M. Umemoto, K. Kojima, M. Ishino, and M. Bonkohara, "3-dimensional chip stacking for high-density electronic packaging," in *Copper Interconnects, New Contact Metallurgies/* Structures, and Low-k Interlevel Dielectrics. Pennington, NJ: ECS, 2003, pp. 264–269.

- [8] J. H. Wu and J. A. del Alamo, "A through-wafer interconnect in silicon for RFICs," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1765–1771, Nov. 2004

- [9] Z. Wang, L. Wang, N. T. Nguyen, W. A. H. Wien, H. Schellevis, P. M. Sarro, and J. N. Burghartz, "Silicon micromachining of high aspect ratio, high-density through-wafer electrical interconnects for 3-D multichip packaging," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, pp. 615–622, Aug. 2006.

- [10] K. A. Jenkins and C. S. Patel, "Copper-filled through wafer vias with very low inductance," in *Proc. IEEE Int. Interconnect Technol. Conf.*, 2005, pp. 144–146.

- [11] L. L. W. Leung and K. J. Chen, "Microwave characterization and modeling of high aspect ratio through-wafer interconnect vias in silicon substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 8, pp. 2472–2480, Aug. 2005.

- [12] S. Linder, H. Baltes, F. Gnaedinger, and E. Doering, "Fabrication technology for wafer through-hole interconnections and three-dimensional stacks of chips and wafers," in *Proc. IEEE MEMS*, 1994, pp. 349–354.

[13] N. P. Pham, K. T. Ng, M. Bartek, P. M. Sarro, B. Rejaei, and

- [13] N. P. Pham, K. T. Ng, M. Bartek, P. M. Sarro, B. Rejaei, and J. N. Burghartz, "A micromachining post-process module for RF silicon technology," in *IEDM Tech. Dig.*, 2000, pp. 481–484.

- [14] G. M. Adema, L.-T. Hwang, G. A. Rinne, and I. Turlik, "Passivation schemes for copper/polymer thin-film interconnections used in multichip modules," *IEEE Trans. Compon.*, *Hybrids, Manuf. Technol.*, vol. 16, no. 1, pp. 53–59, Feb. 1993.

- [15] M. Vogt, M. Kachel, M. Plötner, and K. Drescher, "Dielectric barriers for Cu metallization systems," *Microelectron. Eng.*, vol. 37/38, pp. 181–187, 1997.

- [16] Y. Shacham-Diamand, "Barrier layers for Cu USLI metallization," Electron. Mater., vol. 30, no. 4, pp. 336–344, 2001.

- [17] C.-K. Hu and J. M. E. Harper, "Copper interconnections and reliability," *Mater. Chem. Phys.*, vol. 52, no. 1, pp. 5–16, Jan. 1998.

- [18] T. R. Anthony, "Forming electrical interconnections through semiconductor wafers," J. Appl. Phys., vol. 52, no. 8, pp. 5340–5349, Aug. 1981.

- [19] A. C. West, C.-C. Cheng, and B. C. Baker, "Pulse reverse copper electrodeposition in high aspect ratio trenches and vias," *J. Electrochem. Soc.*, vol. 145, no. 9, pp. 3070–3074, Sep. 1998.

- [20] C. H. Seah, S. Mridha, and L. H. Chan, "DC/pulse plating of copper for trench/via filling," *J. Mater. Process. Technol.*, vol. 114, no. 3, pp. 233– 239, Aug. 2001.

**Joyce H. Wu** received the B.S.E. degree in electrical engineering from the University of Michigan, Ann Arbor, in 1996 and the S.M. and Ph.D. degrees in electrical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 2000 and 2006, respectively.

From 1996 to 1998, she was a Failure Analysis Engineer with Intel Corporation. She was also previously with Toshiba Corporation, Yokohama, Japan, and Hitachi Central Research Laboratory, Tokyo, Japan. She is currently with Pixtronix, Inc., Andover,

MA, where she designs and characterizes MEMS for low-power displays.

**Jesús A. del Alamo** (S'79–M'85–SM'92–F'06) received the Telecommunications Engineer degree from the Polytechnic University of Madrid, Madrid, Spain, in 1980 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1983 and 1985, respectively.

From 1985 to 1988, he was with NTT LSI Laboratories, Atsugi, Japan. Since 1988, he has been with the Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology (MIT), Cambridge, where he is currently a Donner

Professor and a MacVicar Faculty Fellow. His current research interests are on microelectronic technologies for communications and logic processing. He has a particular interest in Si LDMOS, CMOS, GaAs PHEMTs, and GaN HEMTs for RF power applications and in InGaAs HEMTs as a beyond-the-roadmap semiconductor logic technology. He is also active in online laboratories for science and engineering education.

Dr. del Alamo is a member of the Royal Spanish Academy of Engineering. He currently serves as Editor of the IEEE ELECTRON DEVICE LETTERS. He was the recipient of several teaching awards at MIT, such as the Baker Award, the Edgerton Junior Faculty Achievement Award, the Smullin Award, and the Bose Award. He was an NSF Presidential Young Investigator.